## Abu Dhabi University

$\operatorname{CEN}$  - 466 Advanced Digital Design

# Lab Report 1

## Introduction to VHDL: gates using VHDL, components and port map

Author: Muhammad Obaidullah 1030313 Mohammed Farooq 1007778 Mehdi Ismail 1005689

Supervisor: Dr. Mohammed Assad Ghazal

Section 1

December 8, 2012

#### Abstract

We used VHDL jhardware description language; to work on the CycloneII board of Altera. Our course of jadvanced digital system design; aimed at getting us to apply the logic gates and other equipments and techniques learnt of digital systems applied via VHDL coding. This lab will show us through each of the features and language basics to implement logic gates and see their output on the boards.

#### 1 Introduction

VHDL that stands for <VHSIC (very-high-speed-integrated-circuit) Hardware Description Language>, a language developed initially by US department of defense to to have a standard in equipments documentation. The language is similar to the very first language of the kind, Verilog, although verilog is case sensitive and weakly typed language, VHDL is not case sensitive but is a strongly typed language and also influenced verilog to adopt open standard after noticing the success of VHDL. We learnt and used VHDL on QuartusII, software of altera for its boards that the lab of university were equiped with. These boards belonged to the CycloneII family of FPGA boards, more specifically the EP2C35F672C6, which are named as EP2C35 identifies the family, 672 after that is the pins on it. FPGA's are Field programmable gate array, meaning they can be programmably designed to create circuits that we previously bought specific chips and implemented.

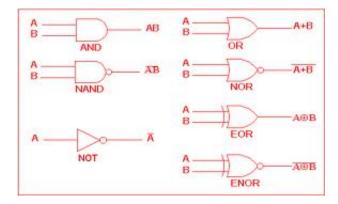

Within the course objectives was to familiarize ourselves with digital logics application into the boards, so as to be able to create any simulation of hardware we might need within a short time frame. To that respect we implemented codes of each of the gates (NOT, AND, OR, XOR, NAND, NOR, XNOR) simulation on the same board simultaneously.

#### 2 Experiment Set-up

The Experiment was set up by opening and setting up the VHDL coding Integrated Development Environment Quartus II. The code was written in the Quartus IDE and then we debugged it. After debugging, We assigned the outputs to the pins on the ALTERA board. These outputs can by anything ranging from LEDs to Buzzers. Additionally, there were some inputs to be assigned to or how else could we get the input from the user. These all pins were assigned by referring to the Datasheet of the ALTERA Cyclone II and were assigned by the Pin Planner inside the Quartus.

## 2 Input AND Gate

| AND Gate                     |      |

|------------------------------|------|

| × 1<br>y 2<br>D <sup>3</sup> | Z=XY |

| INF | UTS | OUTPUT |

|-----|-----|--------|

|     | 0.0 | 001101 |

| ×   | Y   | Z      |

| 0   | 0   | 0      |

| 0   | 1   | 0      |

| 1   | 0   | 0      |

| 1   | 1   | 1      |

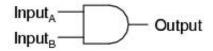

## 2-input AND gate

| А | в | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

| А | в | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

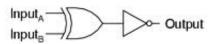

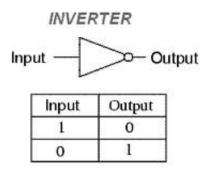

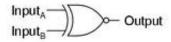

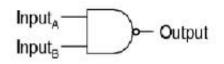

Equivalent gate circuit

| A | в | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

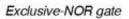

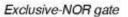

| A | В | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

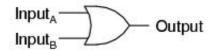

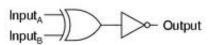

Equivalent gate circuit

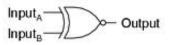

Exclusive-OR gate

| A | в | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

## 3 List of Equipment used

Equipments and materials used during the experiment include

- Computers with Quartus Software.

- CycloneII, Altera Boards

- Power Cable and USB cable to the board

## 4 Procedure

As the first and introductory lab work on the VHDL of the board, we have detailed the process of running the VHDL code and implementing the design. End of this lab report also has the datasheet that the board pins were implemented on.

- Open Quartus.

- Click on Create a new project.

- Click next.

- Create a folder on a directory of your choice and select it as a working directory for you project.

- Name your project and click next.

- Now choose the board to be "EP2C35F672C6".

- Click next and finish.

- Now go to File ¿ New ¿ VHDL File.

- Start writing the code.

|                                              | QUARTUS                                       |

|----------------------------------------------|-----------------------------------------------|

| Start Designing                              | Start Learning                                |

| Designing with Quartus II software           | The audio/video interactive tutorial teaches  |

| requires a project                           | you the basic features of Quartus II software |

| Create a New Project<br>(New Project Wizard) | Open Interactive Tutorial                     |

| Open Existing Project                        |                                               |

| Open Recent Project:                         |                                               |

| Alarm                                        |                                               |

| BCDdecoder<br>FourBitAdder                   |                                               |

|                                              |                                               |

Figure 1: Click on "Create a New Project".

| sitive and must |

|-----------------|

| · · · · · ·     |

| sitive and mast |

|                 |

|                 |

|                 |

|                 |

|                 |

|                 |

|                 |

|                 |

|                 |

|                 |

Figure 2: Choose the directory and name it without spaces and special characters.

| amily: Cyclone I                                                        |                                      |                                                    |                                 | C Show in 'Availa                                                          | ible device' l | ist              |

|-------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|---------------------------------|----------------------------------------------------------------------------|----------------|------------------|

|                                                                         | ſ.                                   |                                                    | -                               | Package:                                                                   | Any            | -                |

| Devices: All                                                            |                                      |                                                    | -                               | Pin count:                                                                 | Any            | •                |

| arget device                                                            |                                      |                                                    |                                 | Speed grade:                                                               | Any            | -                |

| T Auto device sele:                                                     | stad by the Fitte                    |                                                    |                                 |                                                                            |                |                  |

|                                                                         |                                      |                                                    |                                 | Show adva                                                                  |                |                  |

| Specific device s                                                       | elected in 'Avail                    | able devices                                       | list                            | HardCopy of                                                                | compatible o   | nly              |

|                                                                         |                                      |                                                    |                                 |                                                                            |                |                  |

| ilable devices:                                                         |                                      |                                                    |                                 |                                                                            |                |                  |

| ame                                                                     | Core v                               | . LEs                                              | User I/.                        | Memor Er                                                                   | mbed PL        | L                |

| 2C35F484C6                                                              | 1.2V                                 | 33216                                              | 322                             | 483840 70                                                                  | S              |                  |

| 2C35F484C7                                                              | 1.2V                                 | 33216                                              | 322                             | 483840 70                                                                  | S              |                  |

| 2C35F484C8                                                              | 1.2V                                 | 33216                                              | 322                             | 483840 70                                                                  |                |                  |

| 2C35F484I8                                                              | 1.2V                                 | 33216                                              | 322                             | 483840 70                                                                  |                | -                |

| and the ball of the second second second                                |                                      |                                                    |                                 |                                                                            |                |                  |

|                                                                         |                                      |                                                    |                                 |                                                                            | 2              |                  |

|                                                                         |                                      |                                                    |                                 |                                                                            | N              |                  |

|                                                                         |                                      |                                                    |                                 |                                                                            |                |                  |

|                                                                         | 1 41                                 | 111                                                |                                 |                                                                            |                | +                |

| 22C35F672C6<br>22C35F672C7<br>22C35F672C8<br>22C35F672C8<br>22C35F672L8 | 1.2V<br>1.2V<br>1.2V<br>1.2V<br>1.2V | 33216<br>33216<br>33216<br>33216<br>33216<br>22216 | 475<br>475<br>475<br>475<br>222 | 483840 70<br>483840 70<br>483840 70<br>483840 70<br>483840 70<br>483840 70 | )<br>)<br>)    | 4<br>4<br>4<br>4 |

Figure 3: Choose the highlighted board and the Family should be "Cyclone II".

#### 5 VHDL Code for AND Gate

```

-- Lines

- VHDL code for AND gate

--- starting with

--- are comments

library ieee; -- Include all the libraries

5

use ieee.std_logic_1164.all; -- & other built-in namespaces

-- that are typically used in the code

----- Implementation

9

entity AND_ent is

-- Entity is used to declare I/O used in the code

port( x: in std_logic; -- port x is declared as input which accepts when

11

y: in std_logic; -- a logic input/Output value. i.e. 0 or 1

F: out std_logic -- F is declared as Output

13

);

end AND_ent;

15

17

architecture AND_arch1 of AND_ent is

19

- architecture is where actual description lies.

- Two approaches can be used to describe

21

- how our code should be working.

23 begin

25

process(x, y) — process states that perform the below set of code

- when either of x or y changes

begin

27

-- compare to truth table

if ((x='1') and (y='1')) then

29

-- if x and y are equal to 1

F \le '1'; \quad -- Assign 1 to F

31

else

F <= '0';

-- Assign 0 to F

33

end if;

end process;

35

--- end of Architecture

end AND_arch1;

37

architecture AND_arch2 of AND_ent is

39

begin

41

F \le x and y; --- and is a reserved keyword which perform AND

43

end AND_arch2;

45

```

#### 6 VHDL Code for NAND Gate

```

-- Include all the libraries

5

use ieee.std_logic_1164.all; --- & other built-in namespaces

7

-- that are typically used in the code

- -- Implementation

9

entity NAND_ent is

port( x: in std_logic; --- Entity is used to declare I/O used in the code

y: in std_logic; --- port x is declared as input which accepts when

F: out std_logic --- F is declared as Output

11

13

);

end NAND_ent;

17

architecture NAND_arch1 of NAND_ent is

-- architecture is where actual description lies.

19

-- Two approaches can be used to describe

-- how our code should be working.

21

begin

23

process(x, y) — process states that perform the below set of code

- when either of x or y changes

25

begin

-- compare to truth table

27

if (x='1' \text{ and } y='1') then -- here the 'and' compares X and Y

-- Assign 0 to F

F <= '0';

29

else

-- Assign 1

F <= '1';

31

end if;

end process;

33

35 end NAND_arch1;

37

architecture NAND_arch2 of NAND_ent is

39

begin

F \leq x \text{ nand } y;

---- nand is a reserved keyword which perform NAND

41

end NAND_arch2;

43

```

## 7 VHDL Code for NOR Gate

```

port(x: in std_logic; -- port x and y is declared as input which accepts when

y: in std_logic; -- a logic input/Output value. i.e. 0 or 1

F: out std_logic -- F is declared as Output

13

15

);

end NOR_ent;

17

architecture NOR_arch1 of NOR_ent is

- architecture is where actual description lies.

21

- Two approaches can be used to describe

-- how our code should be working.

23

begin

25

process(x, y) — process states that perform the below set of code

- when either of x or y changes

27

begin

- compare to truth table

29

if (x='0' \text{ and } y='0') then

--- if x and y is equal to 0, '=' is comparison operator

31

F \ll '1'; -- Assign 1 to F

33

else

F \ll 0'; -- Assign 0 to F \gg is assignment operator

35

end if;

end process;

end NOR_arch1; --- end of Architecture

39

architecture NOR_arch2 of NOR_ent is

begin

41

F \le x nor y; --- nor is a reserved keyword which perform NOR

43

end NOR_arch2;

45

47

```

## 8 VHDL Code for NOT Gate

```

-- Lines

- VHDL code for NOT gate

--- starting with

--- are comments

5

-- Include all the libraries

library ieee;

use ieee.std_logic_1164.all; -- & other built-in namespaces

7

--- that are typically used in the code

— — Implementation

0

11 entity NOT_ent is

-- Entity is used to declare I/O used in the code

port (x: in std_logic; -- port x is declared as input which accepts when

--- a logic input/Output value. i.e. 0 or 1

13

F: out std_logic --- F is declared as Output

);

15

end NOT_ent;

```

```

17

19

architecture NOT_arch1 of NOT_ent is

- architecture is where actual description lies.

21

- Two approaches can be used to describe

-- how our code should be working.

23

begin

25

process(x)

-- process states that perform the below set of code

--- when x changes

27

begin

--- compare to truth table

29

if (x='1') then -- If x = 1

F <= '0'; -- Assign 0 to F which shows the opposite of input

31

else

F <= '1';

33

end if;

end process;

35

--- end of Architecture

37 end NOT_arch1;

architecture NOT_arch2 of NOT_ent is

39

begin

41

F \le not x; --- not is a reserved keyword which perform NOT

43

end NOT_arch2;

45

```

## 9 VHDL Code for OR Gate

```

-- Lines

--- VHDL code for OR gate

2

-- starting with

- — are comments

6 library ieee; -- Include all the libraries

use ieee.std_logic_1164.all; -- & other built-in namespaces

--- that are typically used in the code

—— — Implementation

10

entity OR_ent is

-- Entity is used to declare I/O used in the code

port( x: in std_logic; -- port x is declared as input which accepts when

12

y: in std_logic; -- a logic input/Output value. i.e. 0 or 1

F: out std_logic -- F is declared as Output

14

);

16 end OR_ent;

18

20 architecture OR_arch1 of OR_ent is

-- architecture is where actual description lies.

- Two approaches can be used to describe

22

```

```

-- how our code should be working.

begin

24

process(x, y) — process states that perform the below set of code

26

- when either of x or y changes

begin

28

-- compare to truth table

if ((x='0') and (y='0')) then

30

-- if x and y is equal to 0'=' is comparison operator

F \le '0'; -- Assign 0 to F' \ge is assignment operator in VHDL

32

else

F <= '1';

34

end if;

--- end of Architecture

end process;

36

38 end OR_arch1;

architecture OR_arch2 of OR_ent is

40

begin

42

F \le x or y; --- or is a reserved keyword which perform OR

44

end OR_arch2;

```

## 10 VHDL Code for XNOR Gate

-- Lines -- starting with 2 --- are comments 4 library ieee; --- Include all the libraries

use ieee.std\_logic\_1164.all; --- & other built-in namespaces 6 -- that are typically used in the code - -- Implementation 10 entity XNOR\_ent is -- Entity is used to declare I/O used in the code 12 port ( x: in std\_logic; -- port x is declared as input which accepts when y: in std\_logic; --- a logic input/Output value. i.e. 0 or 1

F: out std\_logic --- F is declared as Output 14 ); end XNOR\_ent; 16 18 20 architecture XNOR\_arch1 of XNOR\_ent is -- architecture is where actual description lies. - Two approaches can be used to describe 22 - how our code should be working. 24 begin process(x, y) — process states that perform the below set of code 26 --- when either of x or y changes 28 begin

```

-- compare to truth table

30

if (x/=y) then -- if x is not equal to 0

F \ll '0'; --- Assign 0 to F

32

else

-- Assign 1

F <= '1';

34

end if;

end process;

36

end XNOR_arch1;

--- end of Architecture

38

architecture XNOR_arch2 of XNOR_ent is

40

begin

42

F \le x xnor y; --- xnor is a reserved keyword which perform XNOR

44

end XNOR_arch2;

46

```

### 11 VHDL Code for XOR Gate

```

- -- Lines

- VHDL code for XOR gate -- starting with

- -- are comments

5 library ieee; --- Include all the libraries

use ieee.std_logic_1164.all; -- & other built-in namespaces

-- that are typically used in the code

— — Implementation

9

entity XOR_ent is

11

y: in std_logic; --- a logic input/Output value. i.e. 0 or 1

F: out std_logic --- F is declared as Output

);

15 end XOR_ent;

17

19 architecture XOR_arch1 of XOR_ent is

- architecture is where actual description lies.

- Two approaches can be used to describe

21

-- how our code should be working.

23 begin

process(x, y) — process states that perform the below set of code

- when either of x or y changes

begin

27

--- compare to truth table

— if x and y not equal to eachother

— Assign 1 to F

if (x/=y) then

29

F <= '1';

else

31

-- else 0 to F

F <= '0';

end if;

33

end process;

```

```

<sup>35</sup> end XOR_arch1; — end of Architecture

architecture XOR_arch2 of XOR_ent is

begin

41 F <= x xor y; — xor is a reserved keyword which perform AND

43 end XOR_arch2;

45 — _______

```

## 12 Results and Discussions

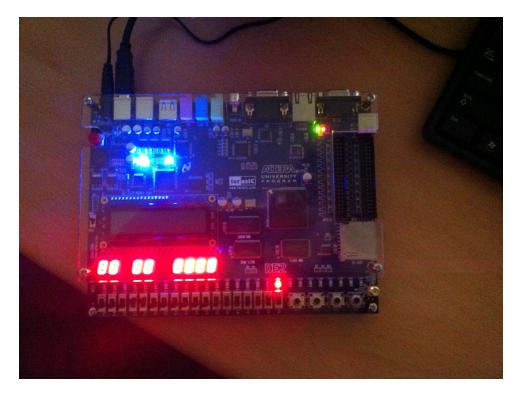

• After compiling the code successful uploading and running of the Altera Board was achieved.

Figure 4: The Board working on AND GATE

## 13 Conclusion

- These were just the basic gates, many gates can be joined together to make up combinational or sequential blocks.

- Solving a problem using FSM is much easier than doing it combinationally.

- FSM allows us to think of the outputs and inputs and build them into a number of stages.

### 14 References

http://www.altera.com/devices/fpga/cyclone2/overview/cy2-overview.html Details on the CycloneII boards, pins, I/O pins availibility. http://esd.cs.ucr.edu/labs/tutorial/ Website that built an idea through the class teaching/showing VHDL coding.

## 15 Team Dynamics

| Report/Member                          | Weight/Grade | Obaidullah | Farooq | Mehdi Ismail |

|----------------------------------------|--------------|------------|--------|--------------|

| Abstract                               | 20%          | 65%        | 15%    | 15%          |

| Introduction                           | 10%          | 0%         | 50%    | 50%          |

| Procedure Part 1                       | 10%          | 100%       | 0%     | 0%           |

| Procedure Part 2                       | 10%          | 0%         | 100%   | 0%           |

| Procedure Part 3                       | 10%          | 0%         | 0%     | 100%         |

| Results Part 1                         | 10%          | 100%       | 0%     | 0%           |

| Results Part 2                         | 10%          | 0%         | 100%   | 0%           |

| Results Part 3                         | 10%          | 0%         | 0%     | 100%         |

| Conclusion                             | 10%          | 0%         | 50%    | 50%          |

| Claimed Contribution                   |              | 33%        | 33%    | 33%          |

| <b>Contribution Validation Penalty</b> | ] [          | 0%         | 0%     | 0%           |

| Overall Contribution                   |              | 33%        | 33%    | 33%          |

| Overall Grade with Quality             | 100%         | 100.0%     | 100.0% | 100.0%       |